【STM32学习笔记】STM32中断

1.异常类型(中断类型)

F103在内核水平上搭载了一个异常响应系统,支持为数众多的系统异常和外部中断。

系统异常8个(不算Reset和HardFault),外部中断有60个。

除个别异常的优先级被定死外,其他异常的优先级都可编程。

异常和外部中断可在标准库文件stm32f10x.h这个头文件找到,在IRQn_Type这个结构体里面包含

了F103系列全部的异常声明。

2.NVIC简介

NVIC 嵌套向量中断控制器,控制着整个芯片中断相关功能,它跟内核紧密耦合,是内核里面的一个外设。

1.NVIC寄存器简介

1 | |

在配置中断的时候我们一般只用ISER、ICER和IP这三个寄存器,ISER用来使能中断,ICER用来失能中断,IP用来设置中断优先级。

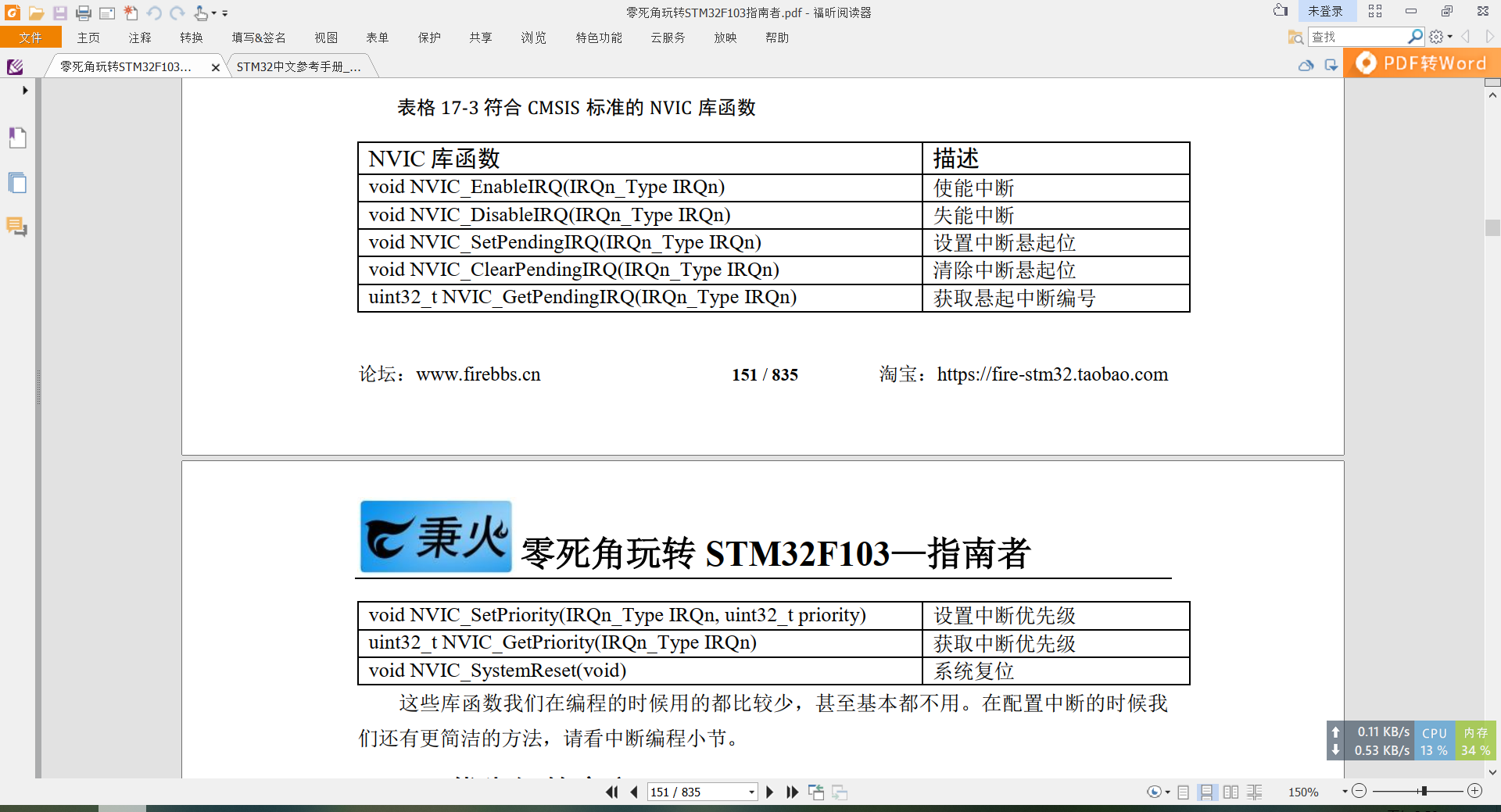

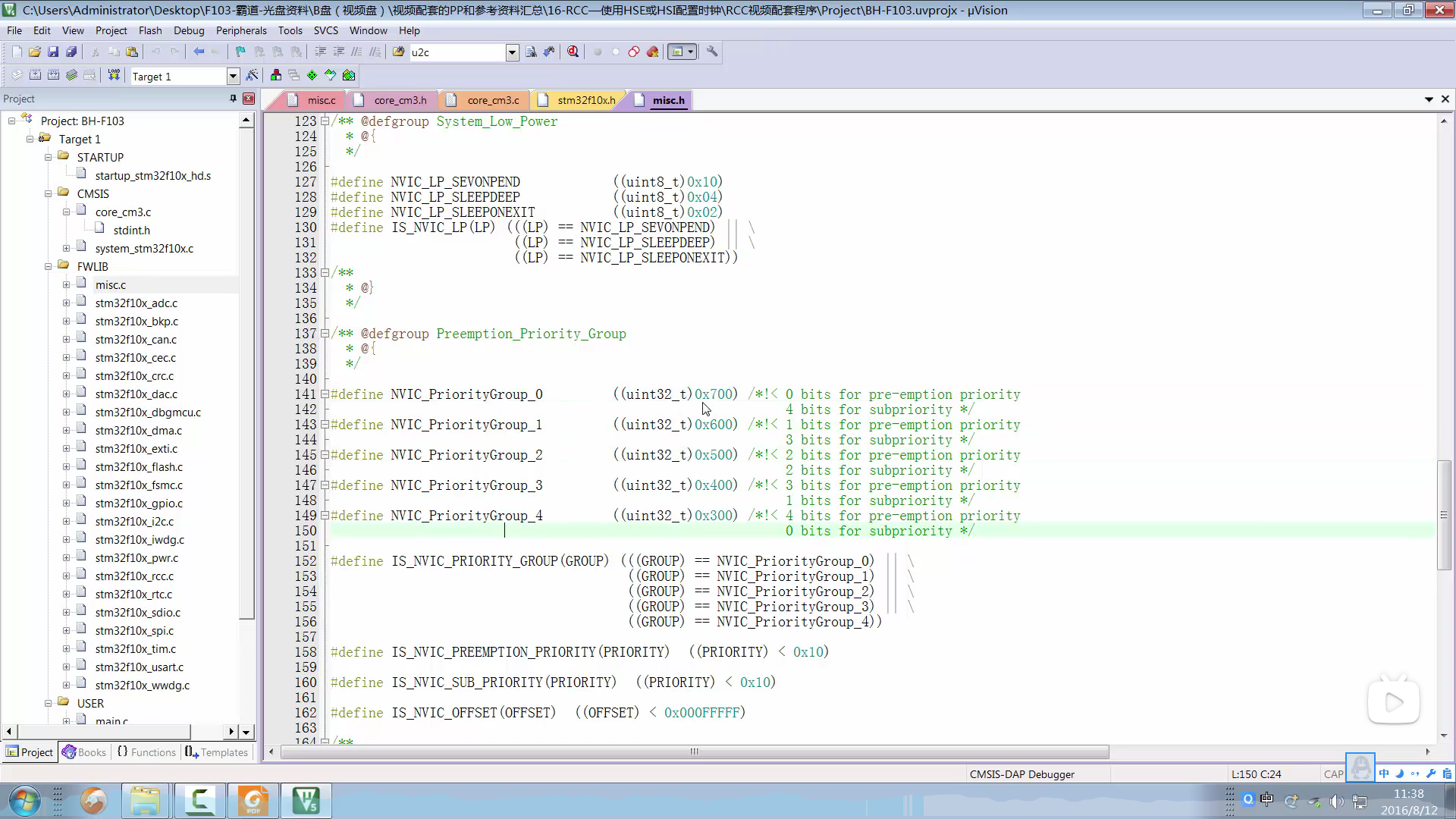

2.NVIC中断配置固件库

在固件库文件core_cm3.h的最后,还提供了NVIC的一些函数,这些函数遵循CMSIS规则,只要是Cortex-M3的处理器都可以使用。

core_cm3.h

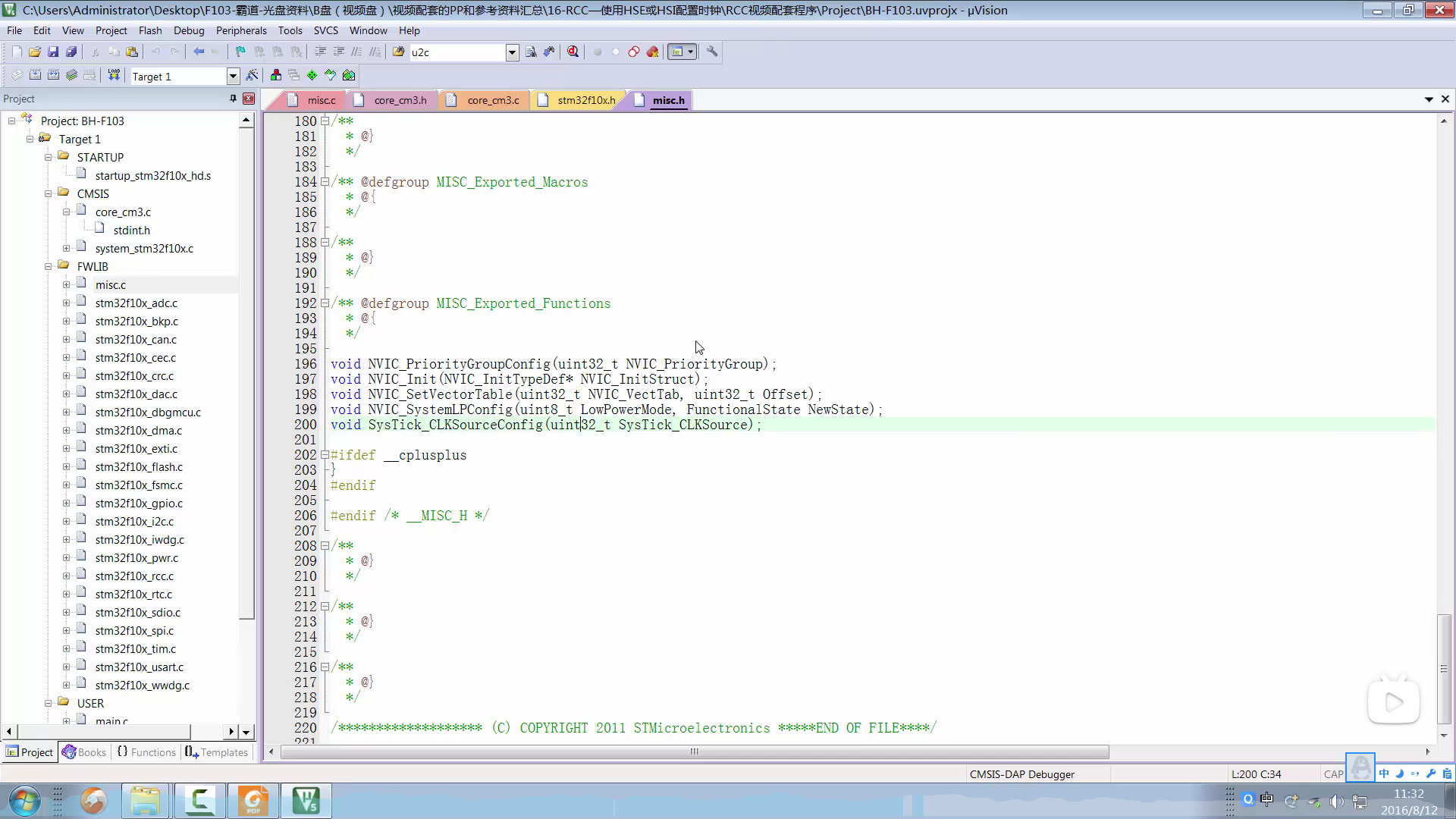

misc.h

3.优先级的定义

1.优先级的定义

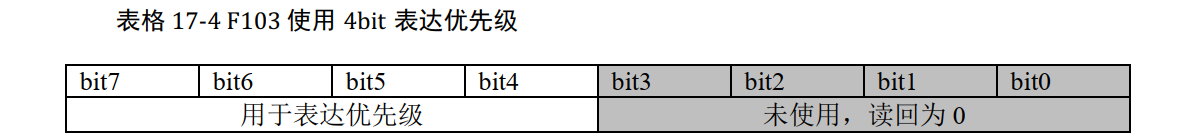

在NVIC中有一个专门的寄存器:中断优先级寄存器NVIC_IPRx,用来配置外部中断的优先级,IPR宽度为8bit,原则上每个外部中断可配置的优先级为0~255,数值越小,优先级越高,但绝大多数CM3芯片都会精简设计,在F103中,只使用了高4bit.

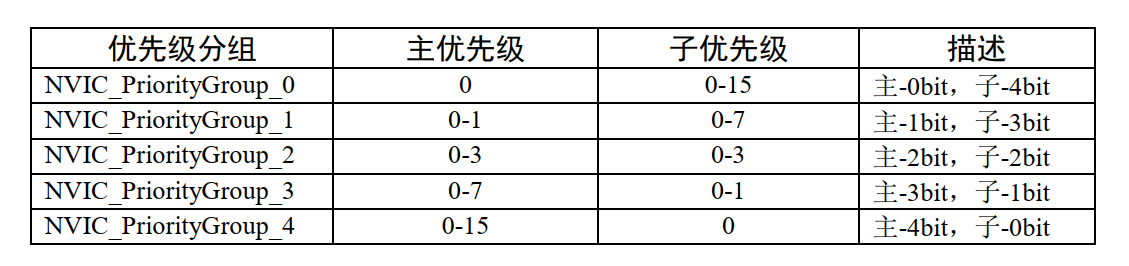

用于表达优先级的这 4bit,又被分组成抢占优先级和子优先级。如果有多个中断同时响应,抢占优先级高的就会抢占抢占优先级低的优先得到执行,如果抢占优先级相同,就比较子优先级。如果抢占优先级和子优先级都相同的话,就比较他们的硬件中断编号,编号越小,优先级越高。

2.优先级分组

优先级的分组由内核外设 SCB 的应用程序中断及复位控制寄存器 AIRCR 的PRIGROUP[10:8]位决定, F103 分为了 5 组,具体如下:主优先级=抢占优先级.

设置优先级分组可调用库函数 NVIC_PriorityGroupConfig()实现,有关 NVIC 中断相关的库函数都在库文件 misc.c 和 misc.h 中。

3.中断编程

1-使能中断请求

这个具体由每个外设的相关中断使能位控制。比如串口有发送完成中断,接收完成中断,这两个中断都由串口控制寄存器的相关中断使能位控制。

2-配置中断优先级分组

调用NVIC_PriorityGroupConfig()这个函数,配置分组。

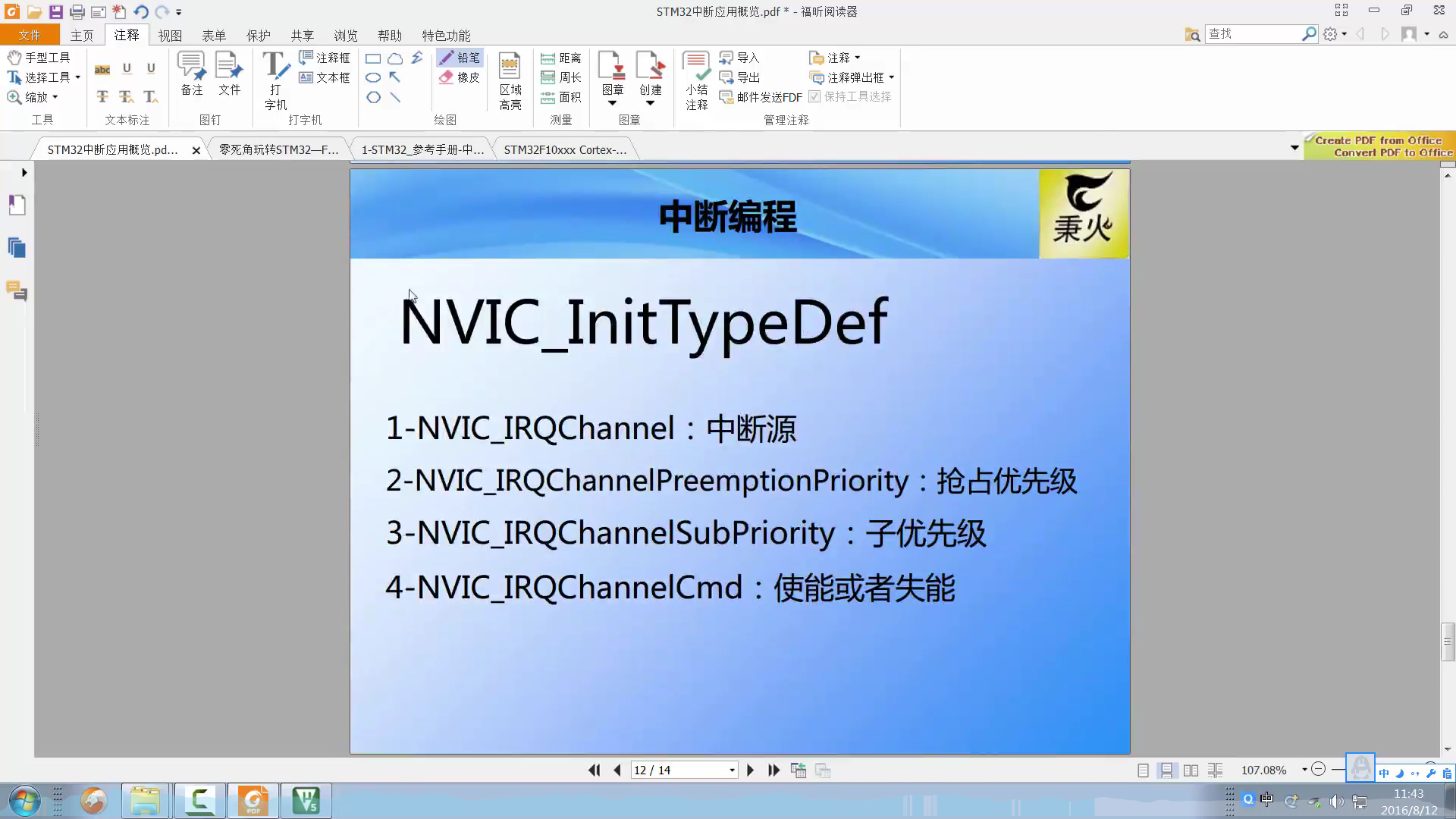

3-配置NVIC寄存器,初始化NVIC_InitTypeDef

NVIC_IRQChannel:中断源

NVIC_IRQChannelPreemptionPriority:抢占优先级

NVIC_IRQChannelSubPriority:子优先级

NVIC_IRQChannelCmd:使能或者失能

4-编写中断服务函数

本博客所有文章除特别声明外,均采用 CC BY-SA 4.0 协议 ,转载请注明出处!